68040: Unterschied zwischen den Versionen

Keine Bearbeitungszusammenfassung |

Keine Bearbeitungszusammenfassung |

||

| Zeile 1: | Zeile 1: | ||

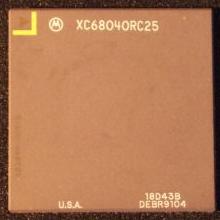

[[Bild:68040.jpg]] | [[Bild:68040.jpg|thumb|Motorola 68040|350px|right]] | ||

Der Motorola 68040 ist ein [[32-Bit]]-Mikroprozessor der Firma Motorola. Er verfügt in der vollen Version über zwei integrierte MMUs (gemäß der Harvard-Architektur) und eine dem Motorola 68881/68882 fast vollständig kompatible FPU, sowie einem Level-1-Cache von 4 KB für jeweils Daten und Instruktionen. Damit leistet er im Integer-Bereich etwa doppelt so viel als ein gleich getakteter Motorola 68030. Die integrierte FPU ist mehr als doppelt so effizient als ein Motorola 68882. Sie folgt dabei dem IEEE 754 Floating Point Standard und beinhaltet keine Logik für trigonometrische Funktionen, diese müssen in Software nachgebildet werden. | |||

== Varianten == | |||

* 68040 - vollständige CPU mit FPU und MMU | |||

* 68LC040 - deaktivierte FPU, MMU vorhanden | |||

* 68EC040 - FPU und MMU deaktiviert | |||

* 68040V - "Low Voltage"-Variante des 68LC040 | |||

== Technische Merkmale == | |||

{| class="wikitable" class="prettytable" | |||

|- | |||

| Arbeitsfrequenzen | |||

| 10 MHz, 20 MHz, 25 MHz, 33 MHz, 40 MHz | |||

|- | |||

| Betriebsspannung || | |||

* Vcore 5 V | |||

* Vcore 3,3 V (68040V) | |||

* I/O 5 V | |||

|- | |||

| Arbeitstemperatur | |||

| -40 -°C bis 70 -°C | |||

|- | |||

| Herstellungsprozess | |||

| static-CMOS 0,6μm | |||

|- | |||

| Bauweise | |||

| CQUAD 184, PGA 179 FG, PGA 182 | |||

|- | |||

| Datenbus | |||

| 32 Bit | |||

|- | |||

| Adressbus | |||

| 32 Bit | |||

|- | |||

| Instructionset | |||

| CISC | |||

|- | |||

| Pipeline | |||

| 6 Stages | |||

|- | |||

| Cache || | |||

* 4kb DCache | |||

* 4kb ICache | |||

* 64 Entry ATC MMU Buffer (4-fach assoziativ) | |||

|- | |||

| Register || | |||

* 8 Adress Register | |||

* 8 Daten Register | |||

* 2 Status Reister | |||

* 8 Floating Point Data Register mit jeweils 80 Bit Breite | |||

* 1 Floating Point Instruction Register | |||

* 1 Floating Point Status Register | |||

* 1 Floating Point Control Register | |||

|- | |||

| Transistoren | |||

| ~1.170.000 (68040)</br> ~962.000 (68EC040)</br> ~813.000 (68LC040) | |||

|- | |||

| Performance || | |||

* ~29 Mips @ 40 MHz (Herstellerangabe von 44 Mips ist eher unrealistisch) | |||

* ~11 MFlops @ 40 MHz | |||

|} | |||

<hr> | |||

Seite "Motorola 68040". In: Wikipedia, Die freie Enzyklopädie. Bearbeitungsstand: 15. März 2010, 14:17 UTC. URL: http://de.wikipedia.org/w/index.php?title=Motorola_68040&oldid=71913636 (Abgerufen: 21. März 2010, 12:00 UTC) | |||

[[Kategorie:CPU]] | [[Kategorie:CPU]] | ||

Version vom 21. März 2010, 13:01 Uhr

Der Motorola 68040 ist ein 32-Bit-Mikroprozessor der Firma Motorola. Er verfügt in der vollen Version über zwei integrierte MMUs (gemäß der Harvard-Architektur) und eine dem Motorola 68881/68882 fast vollständig kompatible FPU, sowie einem Level-1-Cache von 4 KB für jeweils Daten und Instruktionen. Damit leistet er im Integer-Bereich etwa doppelt so viel als ein gleich getakteter Motorola 68030. Die integrierte FPU ist mehr als doppelt so effizient als ein Motorola 68882. Sie folgt dabei dem IEEE 754 Floating Point Standard und beinhaltet keine Logik für trigonometrische Funktionen, diese müssen in Software nachgebildet werden.

Varianten

- 68040 - vollständige CPU mit FPU und MMU

- 68LC040 - deaktivierte FPU, MMU vorhanden

- 68EC040 - FPU und MMU deaktiviert

- 68040V - "Low Voltage"-Variante des 68LC040

Technische Merkmale

| Arbeitsfrequenzen | 10 MHz, 20 MHz, 25 MHz, 33 MHz, 40 MHz |

| Betriebsspannung |

|

| Arbeitstemperatur | -40 -°C bis 70 -°C |

| Herstellungsprozess | static-CMOS 0,6μm |

| Bauweise | CQUAD 184, PGA 179 FG, PGA 182 |

| Datenbus | 32 Bit |

| Adressbus | 32 Bit |

| Instructionset | CISC |

| Pipeline | 6 Stages |

| Cache |

|

| Register |

|

| Transistoren | ~1.170.000 (68040) ~962.000 (68EC040) ~813.000 (68LC040) |

| Performance |

|

Seite "Motorola 68040". In: Wikipedia, Die freie Enzyklopädie. Bearbeitungsstand: 15. März 2010, 14:17 UTC. URL: http://de.wikipedia.org/w/index.php?title=Motorola_68040&oldid=71913636 (Abgerufen: 21. März 2010, 12:00 UTC)