S3C72K8: Unterschied zwischen den Versionen

Keine Bearbeitungszusammenfassung |

Keine Bearbeitungszusammenfassung |

||

| Zeile 68: | Zeile 68: | ||

* Oscillation Sources | * Oscillation Sources | ||

** Crystal, ceramic, or External RC for system clock | ** Crystal, ceramic, or External RC for system clock | ||

** Main system clock frequency: 0.4 | ** Main system clock frequency: 0.4 MHz-6 MHz | ||

** Subsystem clock frequency: 32,768 kHz | ** Subsystem clock frequency: 32,768 kHz | ||

** CPU clock divider circuit (by 4, 8, or 64) | ** CPU clock divider circuit (by 4, 8, or 64) | ||

| Zeile 78: | Zeile 78: | ||

* Operating Temperature | * Operating Temperature | ||

** | ** - 40°C to 85°C | ||

* Operating Voltage Range | * Operating Voltage Range | ||

Aktuelle Version vom 22. Januar 2023, 23:51 Uhr

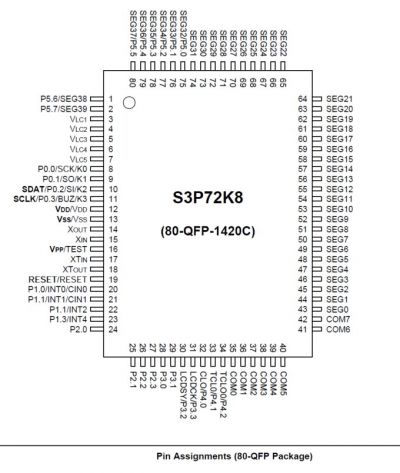

The S3C72K8 singlechip CMOS microcontroller has been designed for high performance using Samsung's newest 4-bit CPU core, SAM48 (Samsung Arrageable Microcontrollers). With a two-channel comparator, up-to-320-dot LCD direct drive capability, 8-bit timer/counter, watchdog timer and serial I/O, the S3C72K8 offers an excellent design solution for a wide variety of applications which require LCD functions.Up to 27 pins of the 80-pin QFP package can be dedicated to I/O. Seven vectored interrupts provide fast response to internal and external events. In addition, the S3C72K8's advanced CMOS technology provides for low power consumption and a wide operating voltage range.

OTP

The S3C72K8 microcontroller is also available is OTP (one time programmable) version, S3P72K8. S3P72K8 microcontroller has an one-chop 8 Kbyte one time programmable EPROM instead of masked ROM. The S3P72K8 is comparable to S3C72K8, both in function and in pin configuration.

Features

- Memory

- 8 K x 8-bit RAM

- 1,024 x 4-bit ROM

- 27 I/O Pins

- Input only: 4 pins

- I/O: 15 pins

- Output: maximum 8 pins for 1-bit level output (sharing with segment driver outputs)

- Comparator

- Two channel mode: internal reference (4-bit resolution)

- One channel mode: external reference

- LCD Controller/Driver

- 40 segments and 8 common terminals

- 3, 4 and 8 common selectable

- Internal resistor circuit for LCD bias

- All dot can be switched on/off

- 8-Bit Basic Timer

- 4 interval timer functions

- Watchdog timer

- 8-Bit Timer/Counter

- Programmable 8-bit timer

- External event counter

- Arbitrary clock frequency output

- External clock signal divider

- Serial I/O interface clock generator

- 8-Bit Serial I/O Interface

- 8-bit transmit/receive mode

- 8-bit receive only mode

- LSB-first or MSB-first transmission selectable

- Internal or external clock source

- Bit Sequential Carrier

- Support 16-bit serial data transfer in arbitrary format

- Watch Timer

- Timer interval generation: 0.5 s, 3.9 ms at 32,768 Hz

- Four frequency outputs to BUZ pin

- Clock source generation for LCD

- Interrupts

- Three internal vectored interrupts: INTB, INTT0, INTS

- Four external vectored interrupts: INT0, INT1, INT4, INTK

- Two quasi-interrupts: INT2, INTW

- Memory-Mapped I/O Structure

- Data memory bank 15

- Two Power-Down Modes

- Idle mode (only CPU clock stops)

- Stop mode (main system oscillation stops)

- Subsystem clock stop mode

- Oscillation Sources

- Crystal, ceramic, or External RC for system clock

- Main system clock frequency: 0.4 MHz-6 MHz

- Subsystem clock frequency: 32,768 kHz

- CPU clock divider circuit (by 4, 8, or 64)

- Instruction Execution Times

- 0.67 us at 6 MHz (minimum)

- 0.95 ms at 4.19 MHz (minimum)

- 122 ms at 32,768 kHz (minimum)

- Operating Temperature

- - 40°C to 85°C

- Operating Voltage Range

- 2.0 V to 5.5 V

Package Type

- 80-pin QFP