SciSys Junior Chess: Unterschied zwischen den Versionen

Erscheinungsbild

Keine Bearbeitungszusammenfassung |

Keine Bearbeitungszusammenfassung |

||

| Zeile 12: | Zeile 12: | ||

| Prozessortyp = [[4 Bit]] | | Prozessortyp = [[4 Bit]] | ||

| Takt = 0,4 MHz | | Takt = 0,4 MHz | ||

| RAM = | | RAM = 160 x 4 Bit | ||

| ROM = | | ROM = 2176 x 10 Bit | ||

| Bibliothek = - | | Bibliothek = - | ||

| Programmierer = [[Taylor, Mark]] & [[Levy, David]] | | Programmierer = [[Taylor, Mark]] & [[Levy, David]] | ||

Aktuelle Version vom 8. Januar 2024, 21:11 Uhr

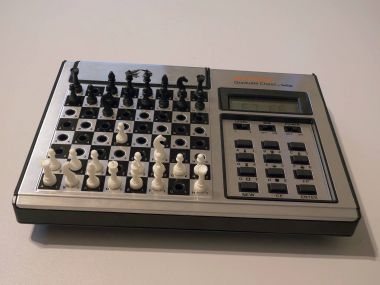

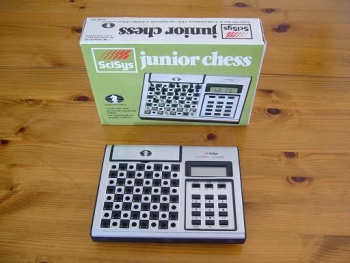

| SciSys Junior Chess | |||

|---|---|---|---|

|

|||

| Hersteller | SciSys | ||

| Markteinführung | 1981 | ||

| CElo | ca. 750 | ||

| Programmierer | Taylor, Mark & Levy, David | ||

| Prozessor | Takt | RAM | ROM |

| Hitachi HD44801 (singlechip) | 0,4 MHz | 160 x 4 Bit | 2176 x 10 Bit |

| Rechentiefe | BT-2450 | BT-2630 | Colditz |

| - | - | - | |

| Bibliothek | - | ||

| Display | 7-Segment LCD Anzeige | ||

| Spielstufen | 2 | ||

| Zugeingabe | Tasten | ||

| Zugausgabe | Display | ||

| Einführungspreis | 89 DM (45 €) | ||

| Prozessortyp | 4 Bit | ||

| Stromversorgung | Batterie 9V Block (für ca. 100 Stunden) | ||

| Maße | 19.0 x 13.8 x 3.0 cm, Schachbrett 9.6 x 9.6 cm, Königshöhe 2 cm | ||

| Verwandt | SciSys Mini Chess, SciSys Graduate Chess | ||

| Sonstiges | |||

| beherrscht Rochade und en passant, aber nicht alle Remisregeln | |||